Ladder Logic hay Ladder Diagram (LD/LAD) là một trong năm ngôn ngữ lập trình PLC được chỉ định sử dụng theo tiêu chuẩn IEC 61131-3. Ladder trực quan hơn nhiều so với hầu hết các ngôn ngữ lập trình, bởi vậy mọi người thường thấy nó dễ học hơn rất nhiều.

Trong hướng dẫn lập trình bằng ngôn ngữ Ladder này, bạn sẽ học mọi thứ cơ bản mà bạn cần biết về ngôn ngữ lập trình PLC sơ đồ bậc thang (LAD). Bạn sẽ có thể bắt đầu tạo các chương trình PLC thực với ngôn ngữ LAD trong hầu hết các phần mềm lập trình PLC.

Xem chi tiết về các dòng sản phẩm PLC: https://mesidas.com/dmsp/plc/

Ladder Logic là gì?

Ladder Logic (còn được gọi là sơ đồ bậc thang hoặc LD/LAD) là một ngôn ngữ lập trình được sử dụng để lập trình PLC (Programmable Logic Controller). Nó là một ngôn ngữ lập trình PLC đồ họa thể hiện các hoạt động logic với ký hiệu tượng trưng. Logic bậc thang được tạo ra từ các nấc thang logic, tạo thành thứ trông giống như một cái thang – do đó có tên là “Ladder Logic” hay “Ladder Diagram”.

Tại sao sử dụng ngôn ngữ LAD để lập trình PLC?

Lý do Ladder Logic là ngôn ngữ được sử dụng để lập trình PLC là bởi các nhà thiết kế, tích hợp hệ thống điều khiển ban đầu đã quen với các mạch điều khiển Relay. Và Ladder Logic là một ngôn ngữ đồ họa bắt trước (mô tả) rất giống với mạch điều khiển Relay. Họ thích sử dụng sơ đồ bậc thang (ladder) thay vì sử dụng các ngôn ngữ lập trình dựa trên văn bản như C, BASIC, Pascal và FORTRON. Một lý do khác khiến sơ đồ bậc thang được sử dụng là bởi nhân viên bảo trì nhà máy đã hiểu cách đọc mạch điều khiển rơ le nên việc sử dụng sơ đồ bậc thang để lập trình PLC có nghĩa là họ có thể dễ dàng khắc phục sự cố hệ thống điều khiển.

LAD giúp bạn hình thành các biểu thức logic ở dạng đồ họa theo yêu cầu để có thể hoàn thành lập trình cho ứng dụng PLC. Chúng đại diện cho các biểu thức điều kiện, đầu vào và đầu ra dưới dạng ký hiệu. Vì vậy việc viết chương trình PLC bằng sơ đồ bậc thang cũng tương tự như việc vẽ mạch điều khiển rơ le.

Sơ đồ bậc thang (LD) là tên chính thức được đưa ra trong tiêu chuẩn lập trình PLC quốc tế IEC-61131. Tuy nhiên, ngày nay các thuật ngữ sơ đồ bậc thang, sơ đồ logic bậc thang, bản vẽ bậc thang, điều khiển bậc thang, mạch bậc thang, sơ đồ logic điều khiển và sơ đồ logic đều được sử dụng để mô tả các mạch logic rơle và lập trình logic bậc thang. Bởi vậy, đừng quá vướng vào định nghĩa cụ thể của từng biểu thức này, chúng thường có nghĩa giống nhau.

Cách viết chương trình LD/LAD (Ladder Diagram)

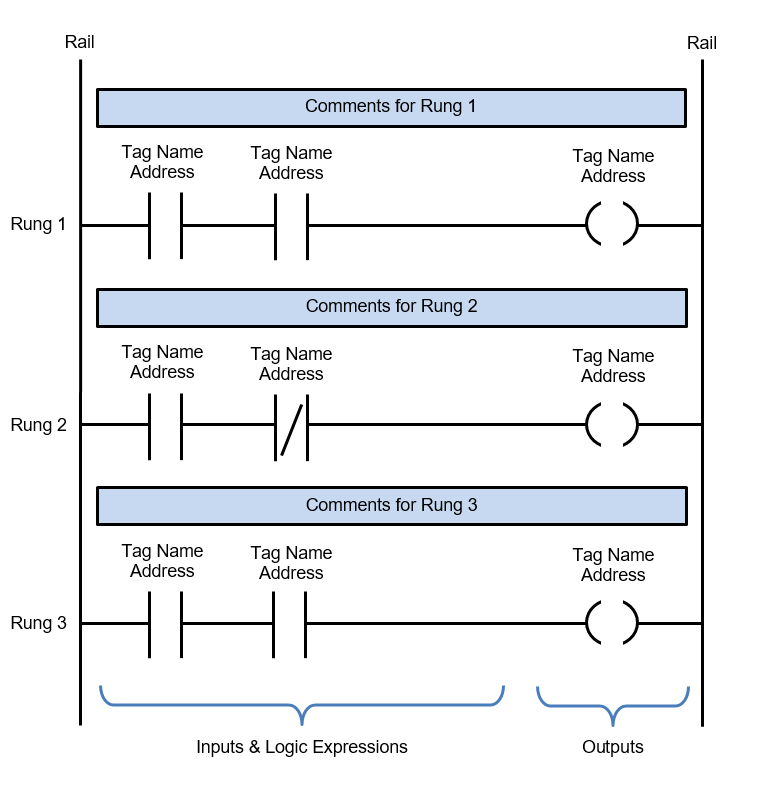

LAD là một ngôn ngữ lập trình đồ họa sử dụng một loạt các đường ray và bậc thang chứa các ký hiệu logic và được kết hợp để tạo thành các biểu thức ra quyết định. Ladder Logic thực sự trông giống như một bậc thang và thường được gọi là lập trình LAD.

Các đường ray trong sơ đồ bậc thang đại diện cho các dây cung cấp của mạch điều khiển logic rơle. Có một đường ray cấp điện áp dương ở phía bên trái và một đường ray cấp điện áp bằng không ở phía bên tay phải. Trong sơ đồ bậc thang, luồng logic là từ thanh ray bên trái sang thanh ray bên phải.

Các bậc thang trong sơ đồ bậc thang đại diện cho các dây kết nối các thành phần của mạch điều khiển rơ le. Trong sơ đồ bậc thang, các ký hiệu được sử dụng để biểu diễn các thành phần rơle. Các ký hiệu được đặt trong bậc thang để tạo thành một mạng lưới các biểu thức logic.

Khi triển khai chương trình logic bậc thang trong PLC, có bảy phần cơ bản của sơ đồ bậc thang cần biết. Chúng là đường ray, bậc thang, đầu vào, đầu ra, biểu thức logic, ký hiệu địa chỉ / tên biến và nhận xét. Một số yếu tố này là cần thiết và những yếu tố khác là bổ sung.

Để giúp hiểu cách vẽ sơ đồ logic bậc thang, mình sẽ trình bày bảy phần cơ bản của biểu đồ bậc thang một cách chi tiết dưới đây:

- Đường ray: có hai đường ray trong một sơ đồ bậc thang được vẽ thành các đường thẳng đứng chạy dọc xuống phần cuối cùng của trang. Ở trong mạch rơ le, chúng sẽ đại diện cho nguồn điện, nơi dòng điện đi từ phía bên trái sang bên tay phải.

- Rungs (nấc thang): các bậc thang được vẽ thành các đường ngang và nối các đường ray với các biểu thức logic. Trong mạch rơle, chúng sẽ đại diện cho các dây kết nối nguồn điện với các thành phần chuyển mạch (nút nhấn, công tắc,..) và rơle.

- Đầu vào: là các tác động điều khiển bên ngoài chẳng hạn như nút nhấn đang được nhấn hoặc công tắc hành trình được kích hoạt. Các đầu vào thực sự được nối cứng với các đầu cuối PLC và được biểu diễn trong sơ đồ bậc thang bằng biểu tượng tiếp điểm thường mở (NO) hoặc thường đóng (NC).

- Đầu ra: là các thiết bị bên ngoài được bật và tắt như động cơ điện hoặc van điện từ. Các đầu ra cũng được nối cứng với các đầu cuối PLC và được biểu diễn trong sơ đồ bậc thang bằng ký hiệu cuộn dây rơ le.

- Biểu thức Logic: được sử dụng kết hợp với các đầu vào và đầu ra để hình thành các quá trình hoạt động điều khiển mong muốn.

- Ký hiệu địa chỉ & tên biến: ký hiệu địa chỉ mô tả cấu trúc, xác định địa chỉ trong bộ nhớ biểu thức logic cho các đầu vào, đầu ra của PLC. Các tên biến là mô tả cho các địa chỉ được phân bổ.

- Nhận xét (chú thích, bình luận): thường được hiển thị ở đầu mỗi bậc thang và được sử dụng để mô tả các biểu thức logic và quá trình hoạt động điều khiển mà bậc thang hoặc các nhóm bậc thang đang thực hiện. Việc hiểu sơ đồ bậc thang trở nên dễ dàng hơn rất nhiều bằng cách sử dụng các nhận xét.

Các biểu tượng (ký hiệu đồ họa) & ý nghĩa trong Ladder Logic

Bởi các biểu tượng (ký hiệu đồ họa) ngôn ngữ lập trình Ladder Logic của các hãng sản xuất PLC sẽ tương tự nhau. Nhờ vậy, mình sẽ sử dụng thư viện biểu tượng của một hãng cụ thể để có thể trình bày được chi tiết và rõ ràng hơn. Mình sẽ sử dụng các tập lệnh Ladder của Step7 Micro/Win mà hãng Siemens cung cấp (các hãng còn lại có thể dựa vào và phân tích tương tự).

Nhập/Xuất giá trị tiếp điểm trong Ladder Logic

Lệnh nhập

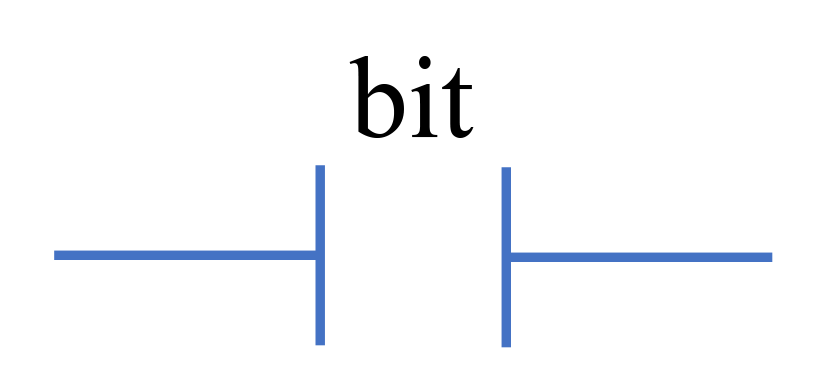

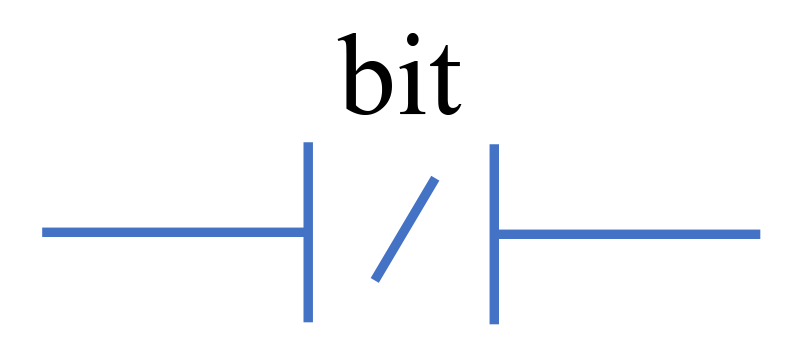

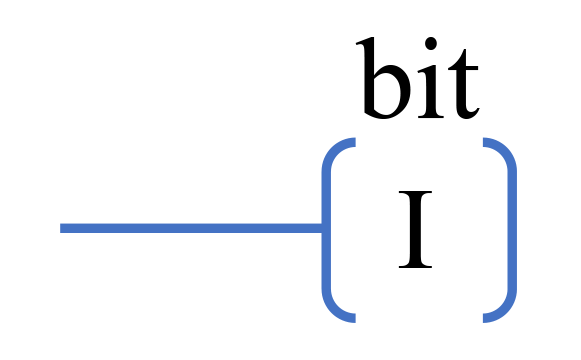

Tiếp điểm thường mở trong LAD

- Tiếp điểm thường mở sẽ được đóng nếu giá trị bit =1

- Toán hạng bit: I,Q,M,SM,T,C,V

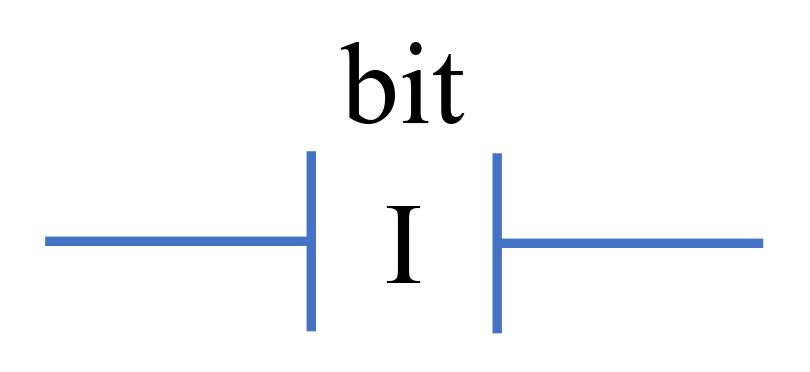

Tiếp điểm thường đóng trong LAD

- Tiếp điểm thường đóng sẽ được mở khi giá trị bit = 1 và ngược lại.

- Toán hạng bit: I,Q,M,SM,T,C,V

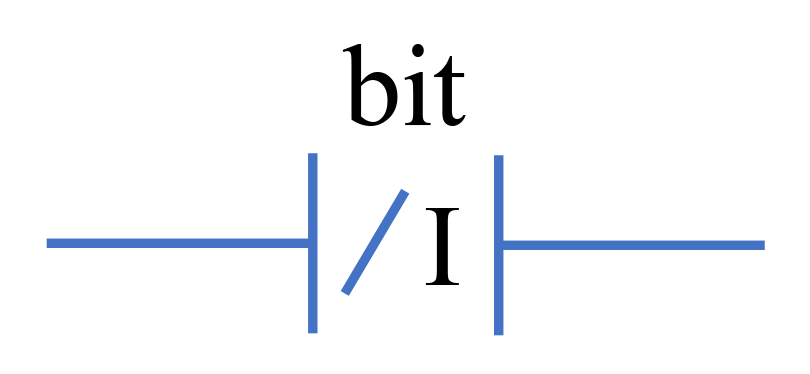

Tiếp điểm thường mở (đóng tức thời) trong LAD

- Tiếp điểm thường mở sẽ được đóng tức thời trong một chu kỳ máy khi giá trị bit = 1

- Toán hạng bit: I

Tiếp điểm thường đóng (mở tức thời) trong LAD

- Tiếp điểm thường đóng sẽ được mở tức thời trong một chu kỳ máy khi giá trị bit = 1

- Toán hạng bit: I

Lệnh xuất

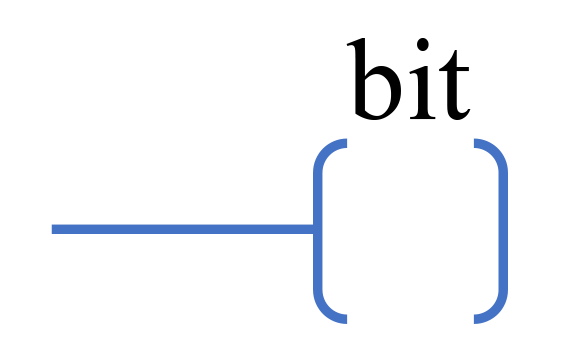

Đầu ra trong LAD

- Cuộn dây đầu ra ở trạng thái kích thích khi có dòng điều khiển đi qua.

- Toán hạng bit: I,Q,M,SM,T,C,V

Đầu ra tức thời trong LAD

- Cuộn dây đầu ra được kích thích tức thời khi có dòng điều khiển đi qua.

- Toán hạng bit: Q

Gán/Xóa giá trị cho tiếp điểm trong Ladder Logic

Lệnh dùng để đóng và ngắt các tiếp điểm gián đoạn đã được thiết kế. Trong dạng LAD, logic điều khiển dòng điện đóng hoặc ngắt các cuộn dây đầu ra. Khi dòng điều khiển tới các cuộn dây thì các cuộn dây đóng hoặc mở các tiếp điểm( hoặc một dãy các tiếp điểm).

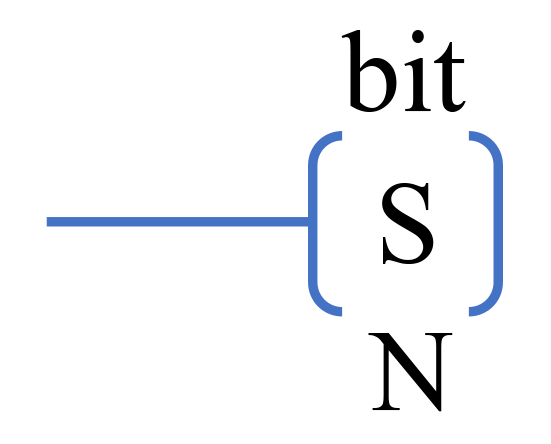

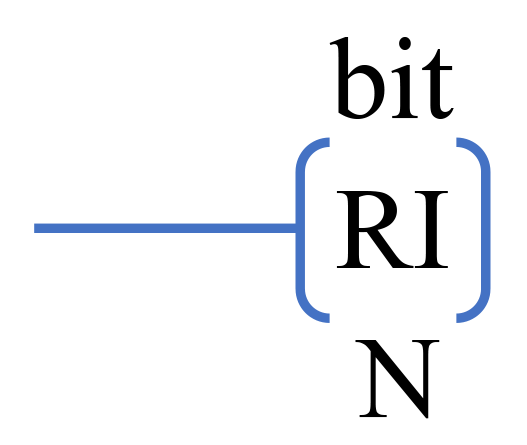

Gán giá trị tiếp điểm trong LAD

Đóng một mảng gồm N các tiếp điểm kể từ bit đặt trước.

Toán hạng:

- bit: I, Q, M, SM, T, C, V.

- N: IB, QB, MB, SMB, VB, AC, Hằng số.

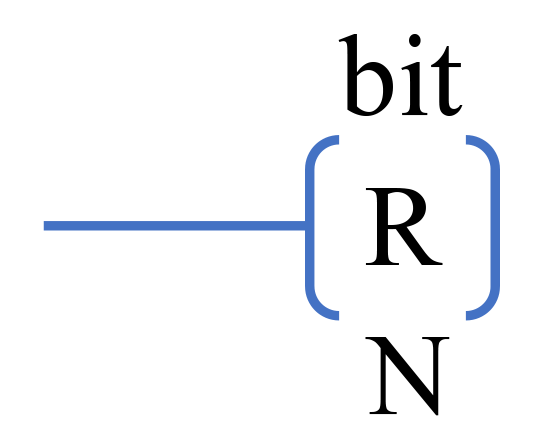

Xóa giá trị tiếp điểm trong LAD

Ngắt một mảng gồm N các tiếp điểm kể từ bit đặt trước.

Toán hạng:

- bit: I, Q, M, SM, T, C, V.

- N: IB, QB, MB, SMB, VB, AC, Hằng số.

Chú thích: Nếu bit đặt trước lại chỉ vào Timer hoặc Counter thì lệnh sẽ xoá bit đầu ra của Timer hoặc Counter đó.

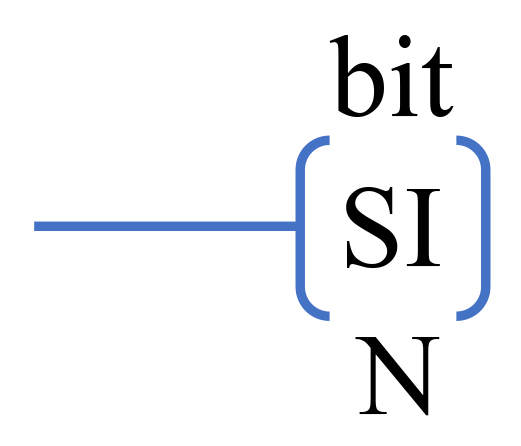

Gán giá trị tiếp điểm tức thời trong LAD

Đóng tức thời một mảng gồm N các tiếp điểm kể từ bit đặt trước

Toán hạng:

- bit: Q.

- N: IB, QB, MB, SMB, VB, AC, Hằng số.

Xóa giá trị tiếp điểm tức thời trong LAD

Ngắt tức thời một mảng gồm N các tiếp điểm kể từ bit đặt trước.

Toán hạng:

- bit: Q.

- N: IB, QB, MB, SMB, VB, AC, Hằng số.

Tiếp điểm đặc biệt trong Ladder Logic

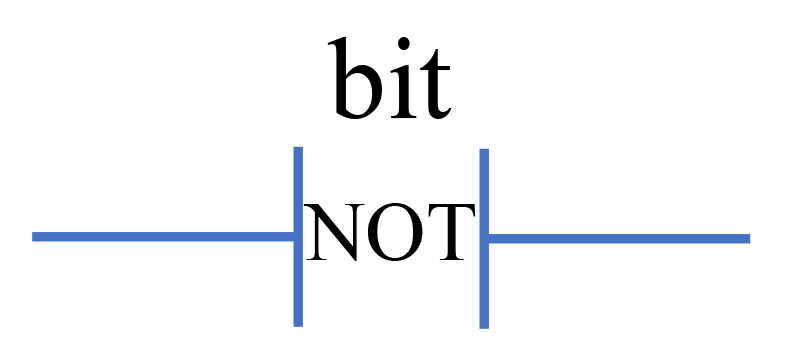

Tiếp điểm đảo trạng thái trong LAD

Tiếp điểm đảo trạng thái của dòng cung cấp. Nếu dòng cung cấp có tiếp điểm đảo thì nó bị ngắt mạch, nếu không có tiếp điểm đảo thì nó thông mạch.

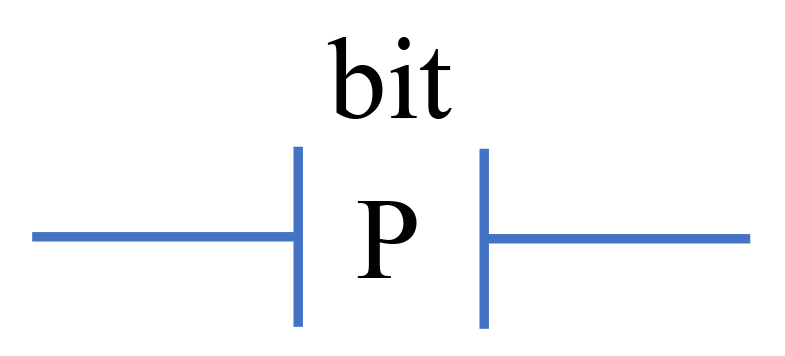

Tiếp điểm lấy sườn dương trong LAD

Tiếp điểm chuyển đổi dương cho phép dòng cung cấp thông mạch trong một vòng quét khi sườn xung điều khiển chuyển từ 0 lên 1

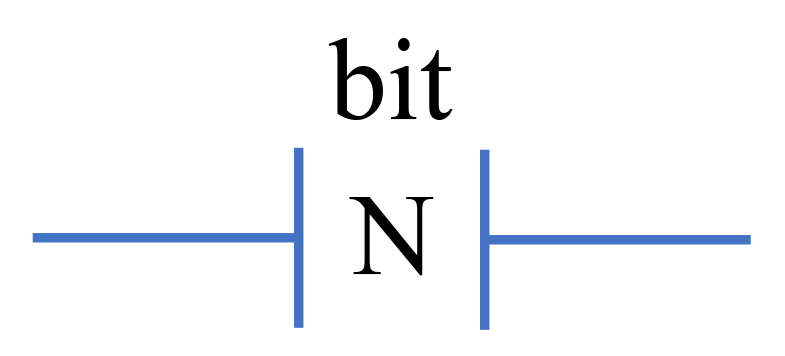

Tiếp điểm lấy sườn âm trong LAD

Tiếp điểm chuyển đổi âm cho phép dòng cung cấp thông mạch trong một vòng quét khi sườn xung điều khiển chuyển từ 1 xuống 0

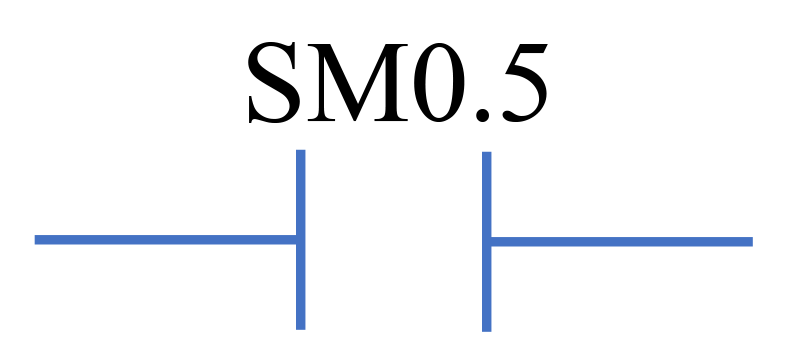

Tiếp điểm tạo xung trong LAD

Tiếp điểm sử dụng bit bộ nhớ đặc biệt tạo dạng sóng vuông tuần hoàn với chu kỳ là 1s (0.5s có xung, 0.5s không có xung)

Timer (bộ định thời gian) trong Ladder Logic

Timer là bộ tạo thời gian trễ giữa tín hiệu vào và tín hiệu ra nên trong điều khiển vẫn thường được gọi là khâu trễ. Có ba kiểu Timer của S7-200 phân biệt với nhau ở phản ứng của nó đối với trạng thái tín hiệu đầu vào ( TON, TOF và TONR ).

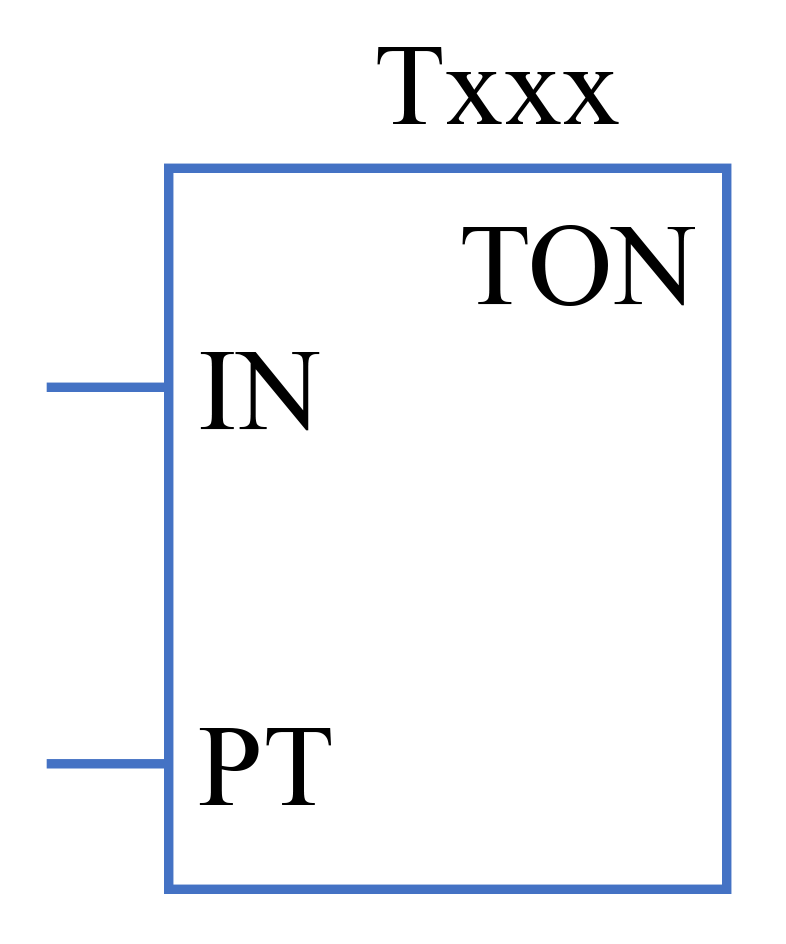

TON trong LAD

Các toán hạng:

- TON: lệnh đếm thời gian tác động đóng trể không nhớ.

- Txxx: Khai báo xxx kiểu TON định độ phân giải có giá trị tra theo bảng.

- IN: đầu vào cho phép lệnh đếm thời gian hoạt động.

Bảng định độ phân giải TON:

| 1 ms | 32.767 s (0.546 min) | T32, T96 |

| 10 ms | 32.767 s (0.546 min) | T33 đến T36, T97 đến T100 |

| 100 ms | 32.767 s (0.546 min) | T37 đến T63, T101 đến T255 |

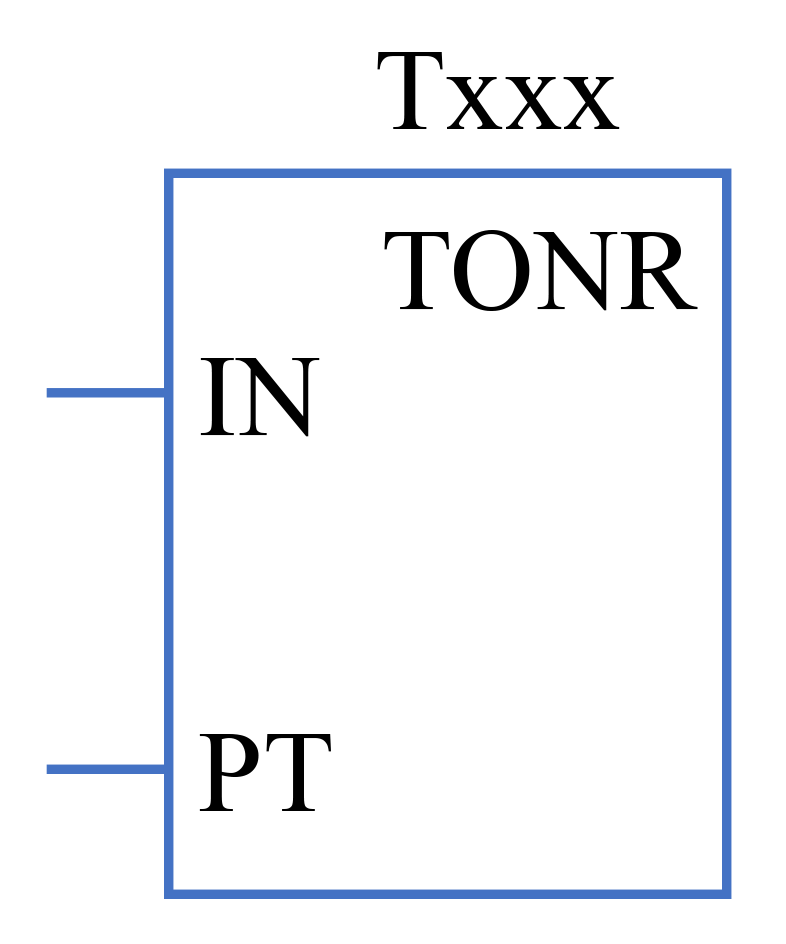

TONR trong LAD

Các toán hạng:

- TONR: lệnh đếm thời gian tác động đóng trể có nhớ.

- Txxx: Khai báo xxx kiểu TONR định độ phân giải có giá trị tra theo bảng

- IN: Đầu vào cho phép lệnh đếm thời gian hoạt động.

- PT: Giá trị đặt trước.

Bảng định độ phân giải TONR:

| 1 ms | 32.767 s (0.546 min) | T0, T64 |

| 10 ms | 32.767 s (0.546 min) | T1 đến T4, T65 đến T68 |

| 100 ms | 32.767 s (0.546 min) | T5 đến T31, T69 đến T95 |

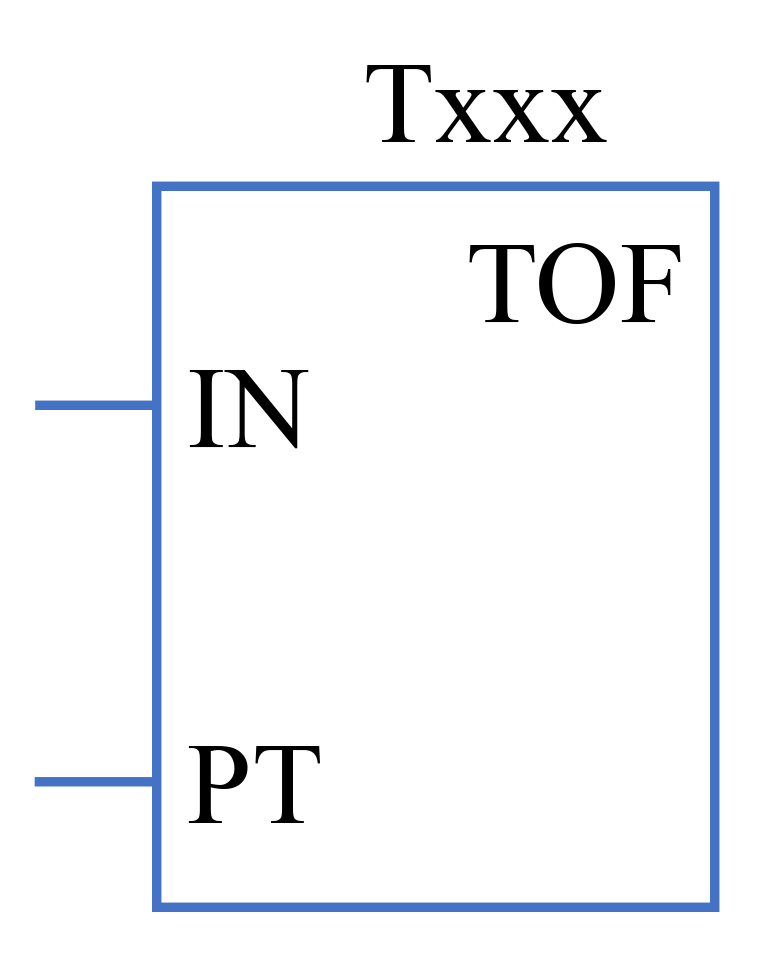

TOF trong LAD

Các toán hạng:

- TOF: Lệnh đếm thời gian tác động mở trể không nhớ.

- Txxx: Khai báo xxx kiểu TOF định độ phân giải có giá trị tra theo bảng.

- IN: đầu vào cho phép lệnh đếm thời gian hoạt động.

- PT: Giá trị đặt trước.

Counter (bộ đếm) trong Ladder Logic

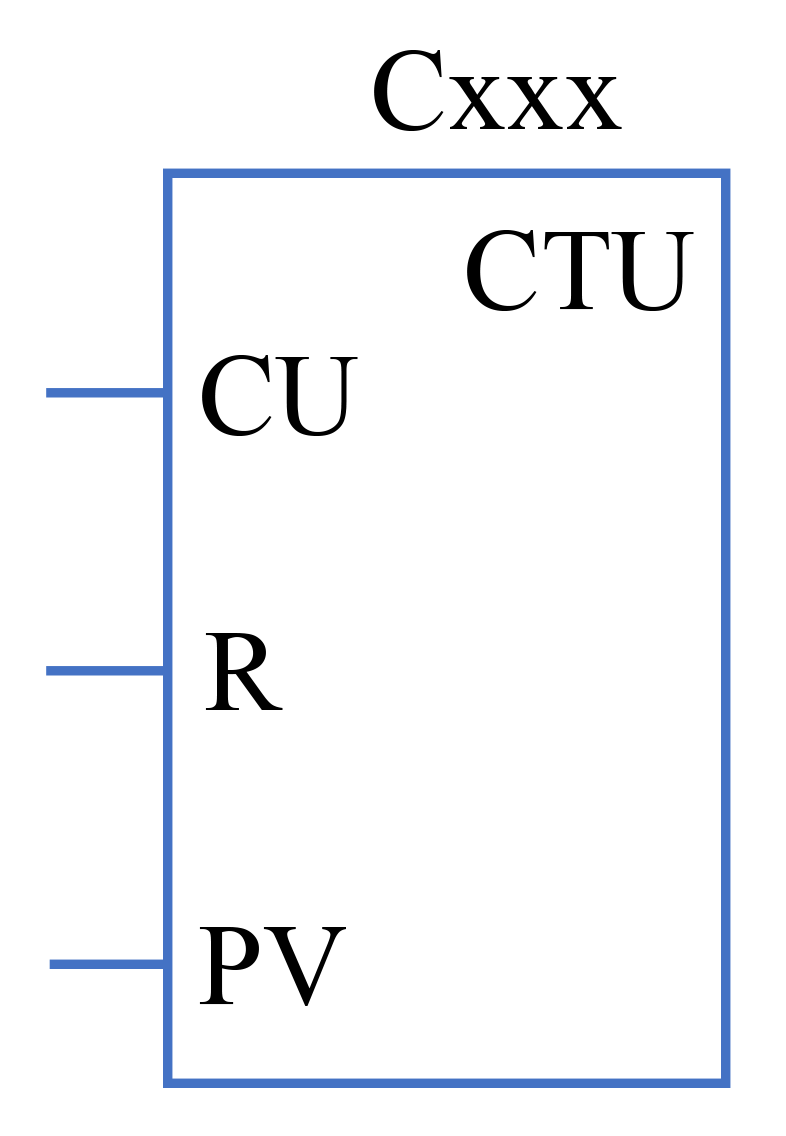

CTU trong LAD

Các toán hạng:

- CTU: Lệnh đếm lên tác động sườn lên.

- Cxxx: Khai báo địa chỉ lệnh, với xxx là số nguyên có giá trị từ 0 đến 255.

- CU ( Count Up): Đầu vào tác động lệnh đếm lên.

- R ( Reset ): Xoá giá trị thanh ghi số đếm về 0.

- PV ( Preset Value ): Giá trị đặt trước, là số nguyên có giá trị đến +32.767.

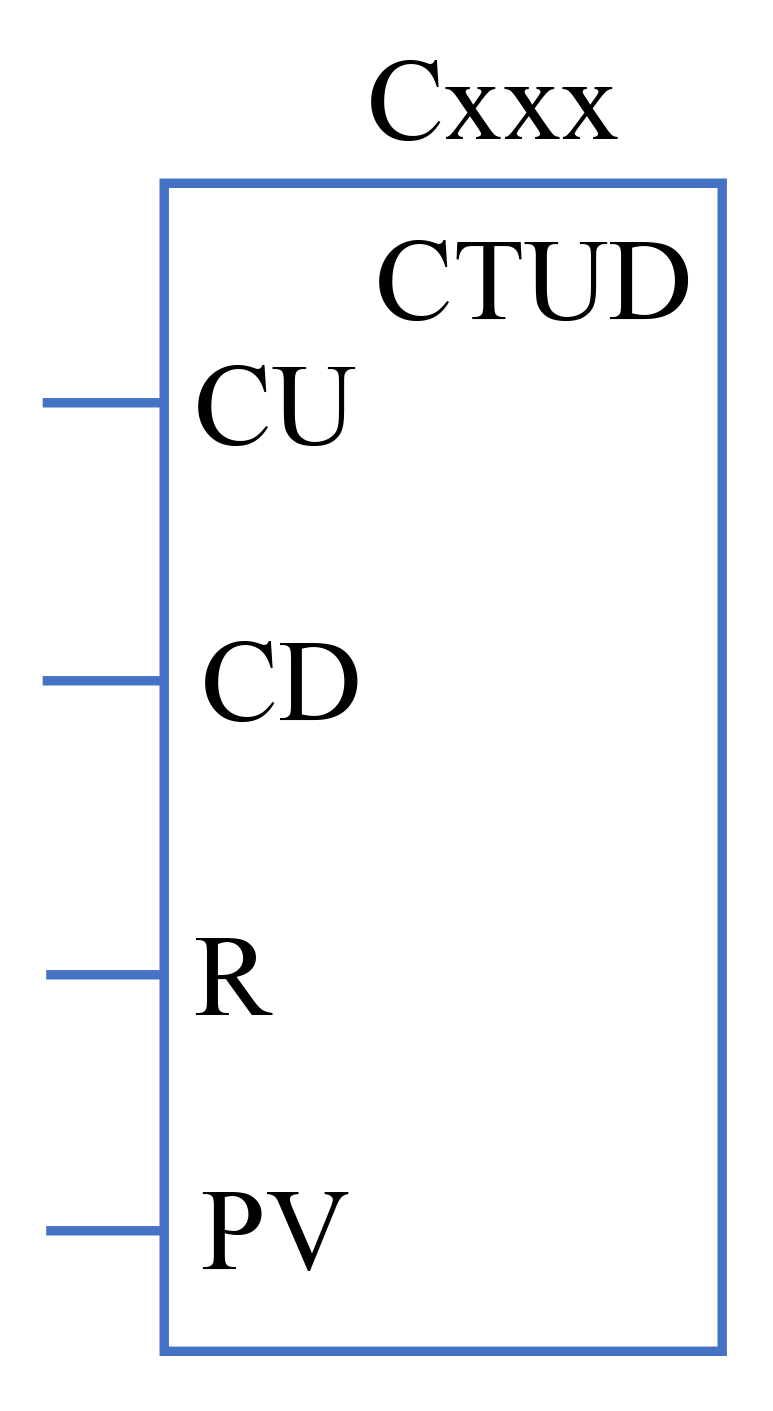

CTUD trong LAD

Các toán hạng:

- CTUD: Lệnh đếm lên xuống tác động sườn lên.

- Cxxx: Khai báo địa chỉ lệnh, với xxx là số nguyên có giá trị từ 0 đến 255.

- CU ( Count Up): Đầu vào tác động lệnh đếm lên.

- CD ( Count Down): Đầu vào tác động lệnh đếm xuống.

- R ( Reset ): Xoá giá trị thanh ghi số đếm về 0.

- PV ( Preset Value ): Giá trị đặt trước, là số nguyên có giá trị từ -32.768 đến +32.767.

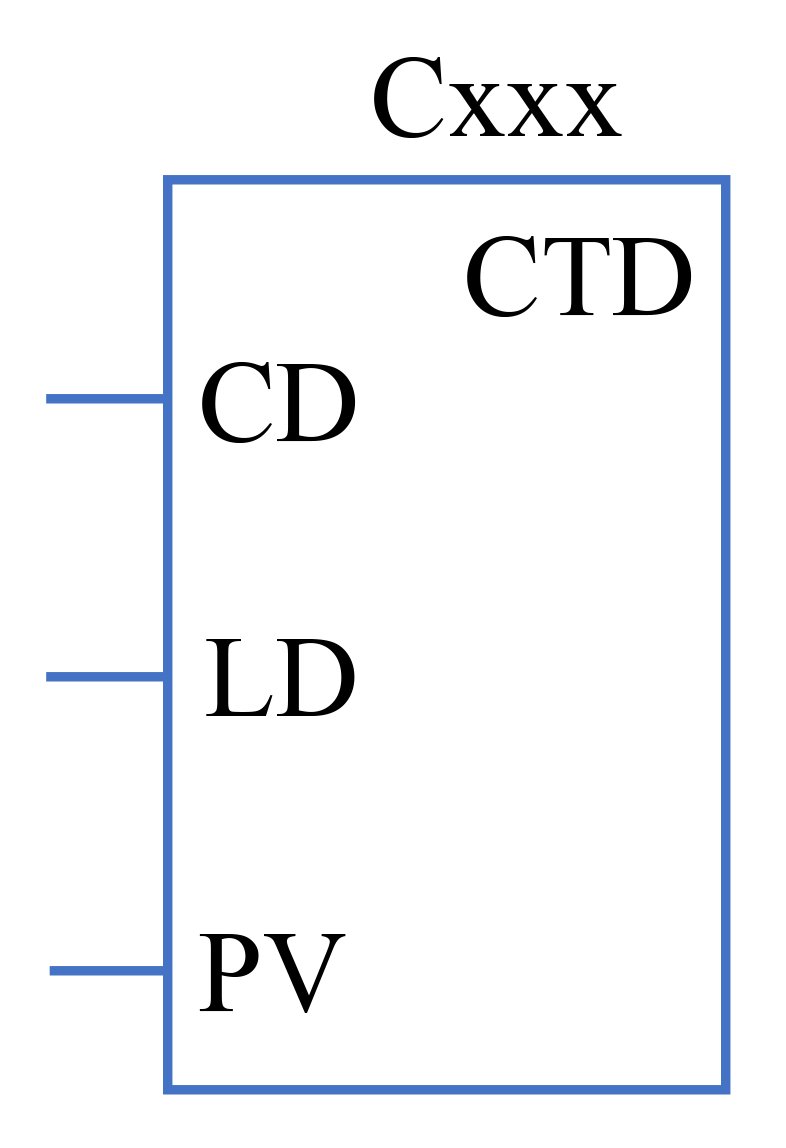

CTD trong LAD

Các toán hạng:

- CTD: Lệnh đếm xuống tác động sườn lên.

- Cxxx: Khai báo địa chỉ lệnh, với xxx là số nguyên có giá trị từ 0 đến 255.

- CD ( Count Down): Đầu vào tác động lệnh đếm xuống.

- LD ( Load ): Nạp giá trị PV vào thanh ghi số đếm.

- PV ( Preset Value ): Giá trị đặt trước, là số nguyên.

Lệnh so sánh trong Ladder Logic

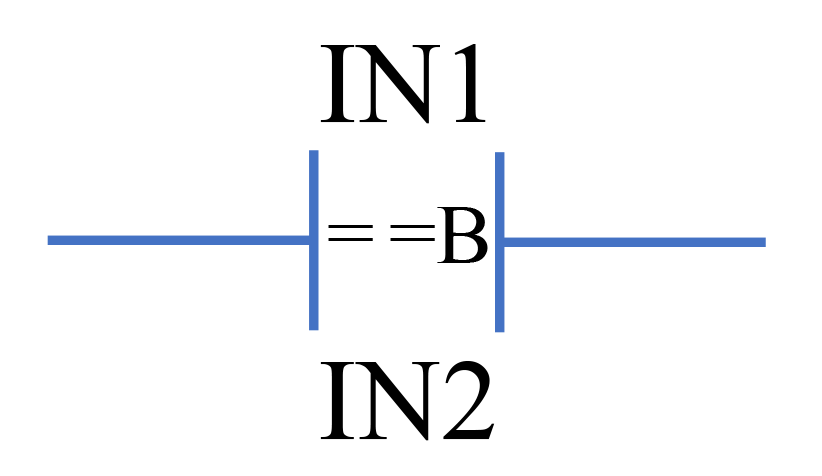

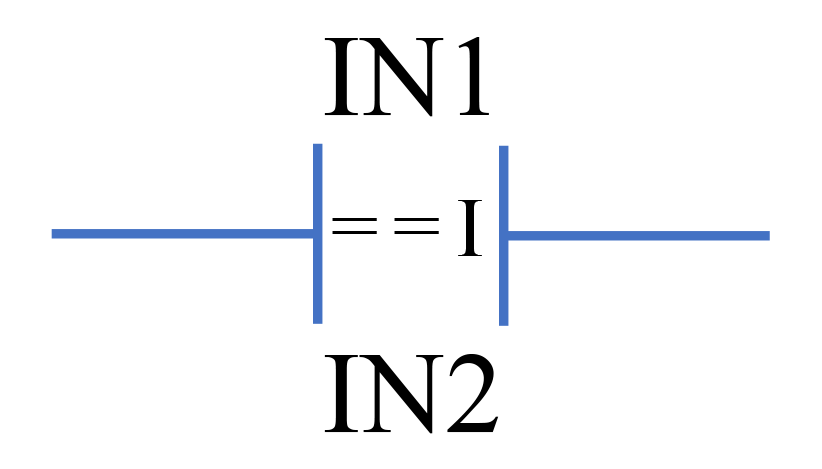

So sánh Byte trong LAD

- Lệnh so sánh theo kiểu Byte ( từ ) được dùng để so sánh hai giá trị IN1 và IN2.

- Trong lệnh so sánh theo kiểu Byte bao gồm: IN1==IN2, IN1>=IN2, IN1<=IN2, IN1<IN2, IN1>IN2, IN1 <>IN2.

- Tiếp điểm đóng nếu phép so sánh là đúng

- Byte được so sánh dạng không dấu.

- Toán hạng đầu vào: IB, QB, MB, SMB, VB, SB, LB, AC, hằng số.

So sánh số nguyên trong LAD

- Lệnh so sánh theo kiểu số nguyên được dùng để so sánh hai giá trị IN1 và IN2.

- Trong lệnh so sánh theo kiểu số nguyên bao gồm: IN1==IN2, IN1 >=IN2, IN1<=IN2, IN1 <IN2, IN1>IN2, IN1 <>IN2.

- Tiếp điểm đóng nếu phép so sánh là đúng

- Số được so sánh dạng có dấu.

- Toán hạng đầu vào: IW, QW, MW, SMW, VW, SW, LW, AC, T, C, hằng số.

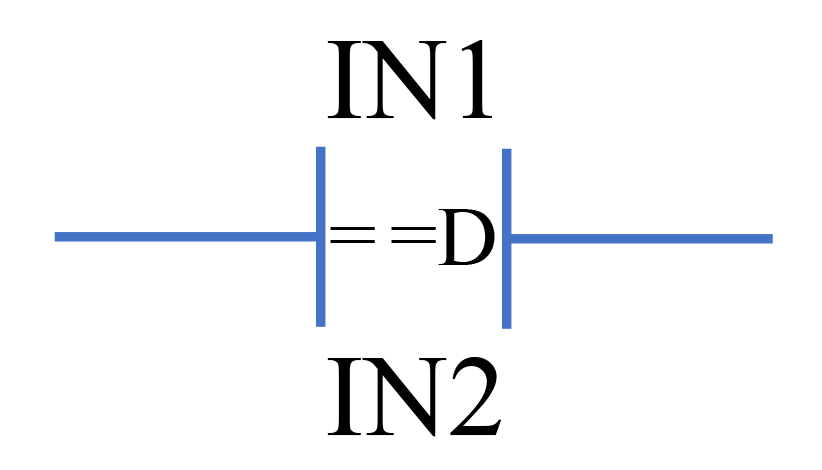

So sánh Double Word trong LAD

- Lệnh so sánh theo kiểu Double Word ( từ kép ) được dùng để so sánh hai giá trị IN1 và IN2.

- Trong lệnh so sánh theo kiểu số nguyên bao gồm: IN1==IN2, IN1 >=IN2, IN1<=IN2, IN1<IN2, IN1>IN2, IN1<>IN2.

- Tiếp điểm đóng nếu phép so sánh là đúng

- Số được so sánh dạng có dấu.

- Toán hạng đầu vào: ID, QD, MD, SMD, VD, SD, LD, AC, hằng số.

MOVE trong Ladder Logic

Trong S7_200 có các hàm Move sau:

- MOV_B: Di chuyển các giá trị cho nhau trong giới hạn 1 Byte

- MOV_W: Di chuyển các giá trị nguyên cho nhau trong giới hạn 1 Word

- MOV_DW: Di chuyển các giá trị nguyên cho nhau trong giới hạn 1 Dword

- MOV_R: Di chuyển các giá trị thực cho nhau trong giới hạn 1 R

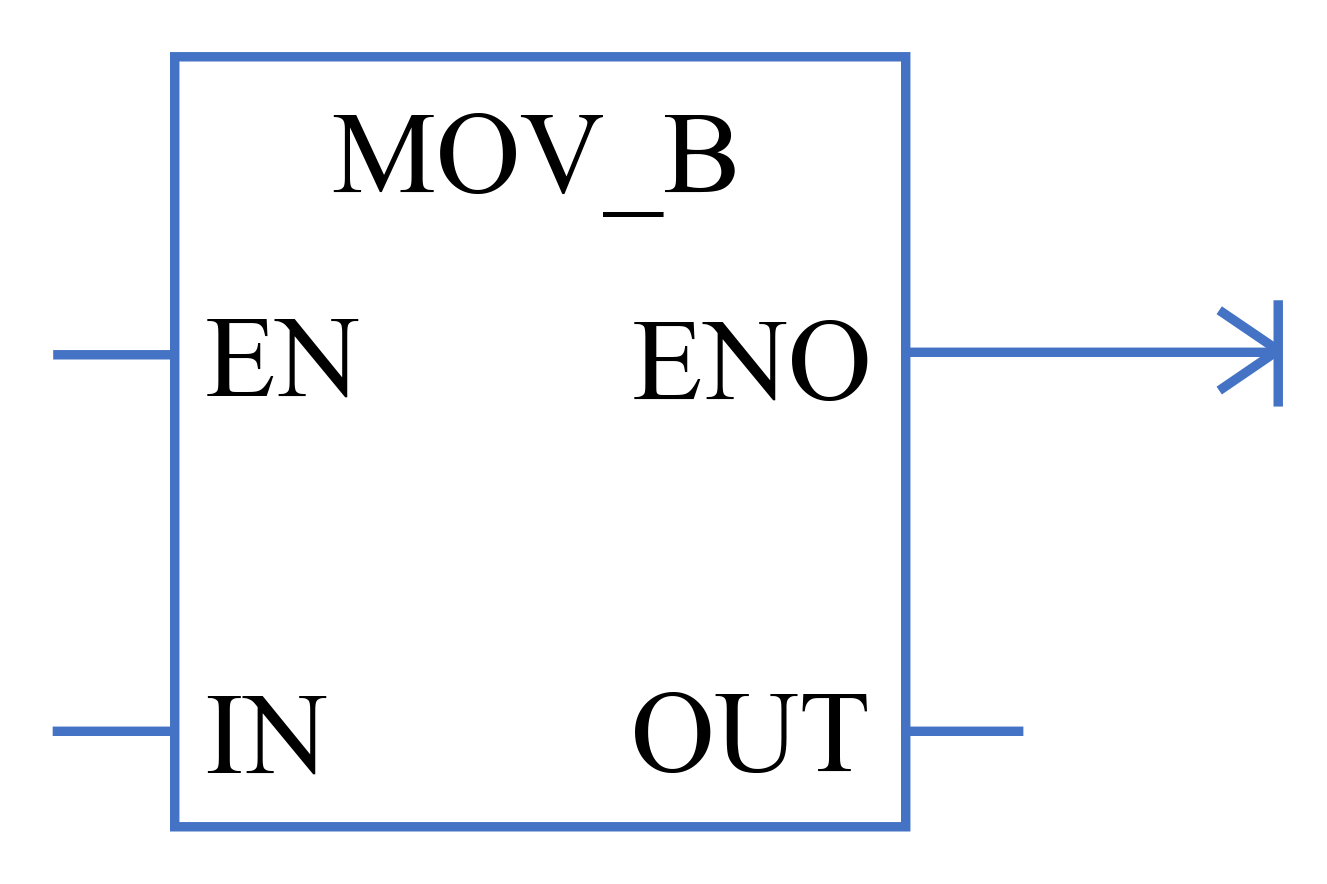

MOV_B trong LAD

- EN: ngõ vào cho phép

- IN Ngõ vào: VB, IB, QB, MB, SB, SMB, LB, AC, Constant, *VD, *LD, *AC

- OUT Ngõ ra: VB, IB, QB, MB, SB, SMB, LB, AC, *VD, *LD, *AC

Khi có tín hiệu ở ngõ cho phép, lệnh sẽ chuyển nội dung của ô nhớ trong (IN) sang ô nhớ trong OUT

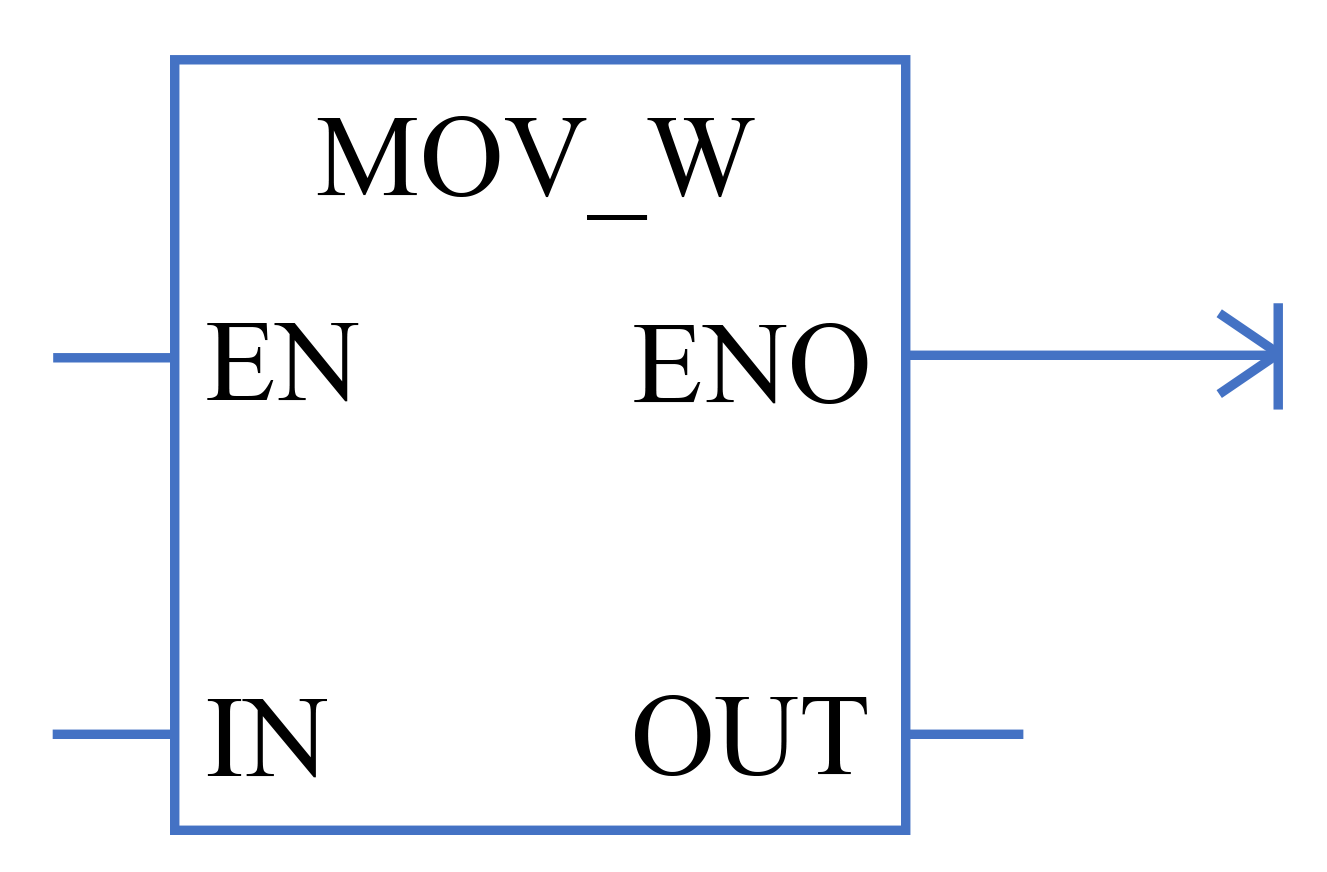

MOV_W trong LAD

- EN: ngõ vào cho phép

- IN Ngõ vào: VW, IW, QW, MW, SW, SMW, LW, T, C, AIW, Constant, AC, *VD,*AC, *LD

- OUT Ngõ ra: VW, T, C, IW, QW, SW, MW,SMW, LW, AC, AQW, *VD,*AC, *LD

Khi có tín hiệu ở ngõ cho phép,lệnh sẽ chuyển nội dung của ô nhớ trong (IN) sang ô nhớ trong OUT

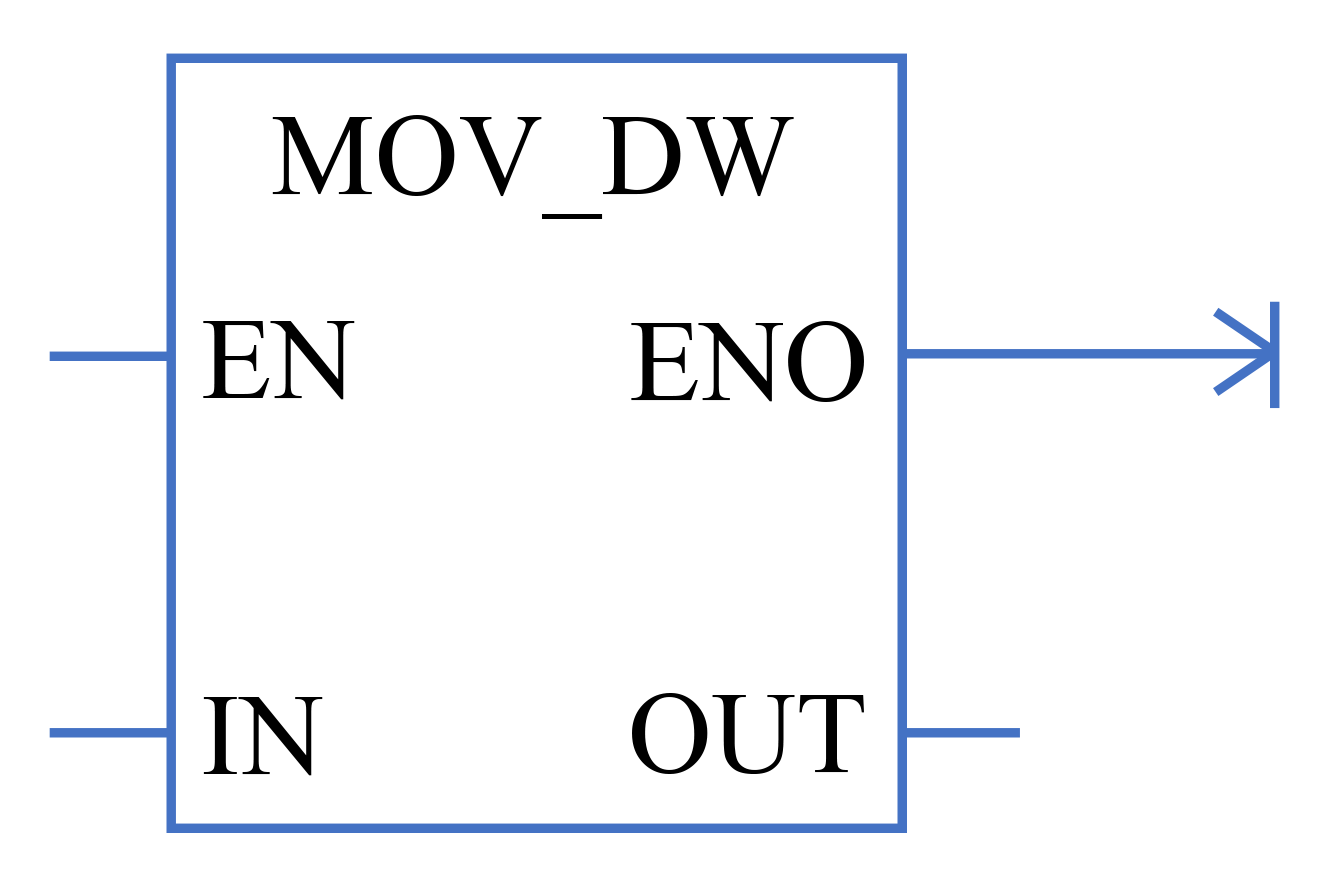

MOV_DW trong LAD

- EN: ngõ vào cho phép

- IN Ngõ vào: VD, ID, QD, MD, SD, SMD, LD, HC, &VB, &IB, &QB, &MB, &SB, &T, &C, &SMB, &AIW, &AQW AC, Constant, *VD, *LD, AC

- OUT Ngõ ra: VD, ID, QD, MD, SD, SMD, LD, AC, *VD, *LD, *AC

Khi có tín hiệu ở ngõ cho phép,lệnh sẽ chuyển nội dung của ô nhớ trong (IN) sang ô nhớ trong OUT

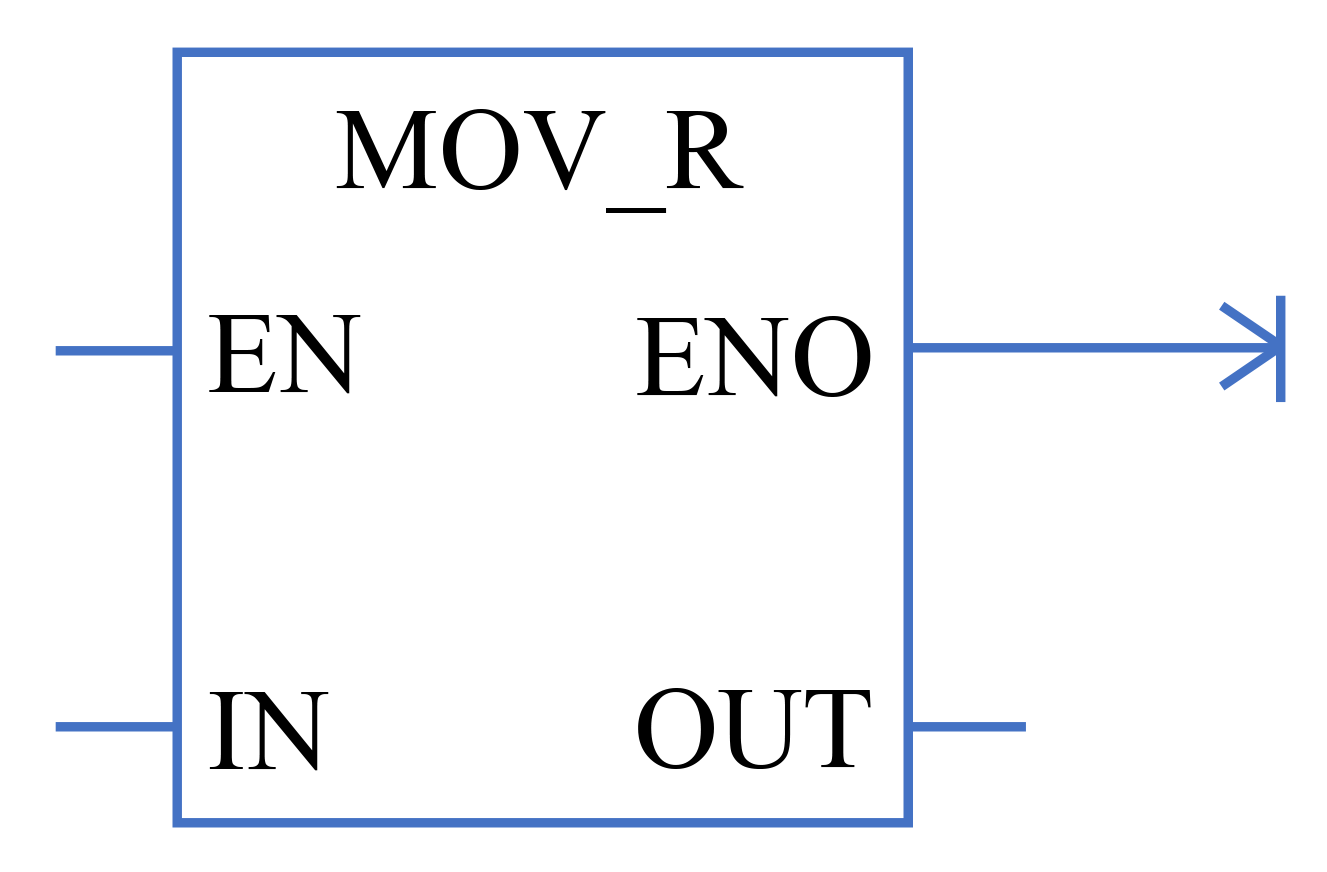

MOV_R trong LAD

- EN: ngõ vào cho phép

- IN Ngõ vào: VD ,ID ,QD ,MD ,SD, SMD, LD, AC, Constant, *VD, *LD, *AC, *LD

- OUT Ngõ ra: VD, ID, QD, MD, SD,SMD, LD, AC, *VD, *LD, *AC,*LD

Khi có tín hiệu ở ngõ cho phép,lệnh sẽ chuyển nội dung của ô nhớ trong (IN) sang ô nhớ trong OUT

Chú ý: Các tín hiệu ngõ vào cũng như ngõ ra của các lệnh Move phải được chọn đúng loại theo đã định như vùng định Dword đối với Move_R và Move_DW… Nếu chọn sai định dạng sai thì chương trình biên dịch cũng bị sai.

Lệnh xoay vòng bit trong Ladder Logic

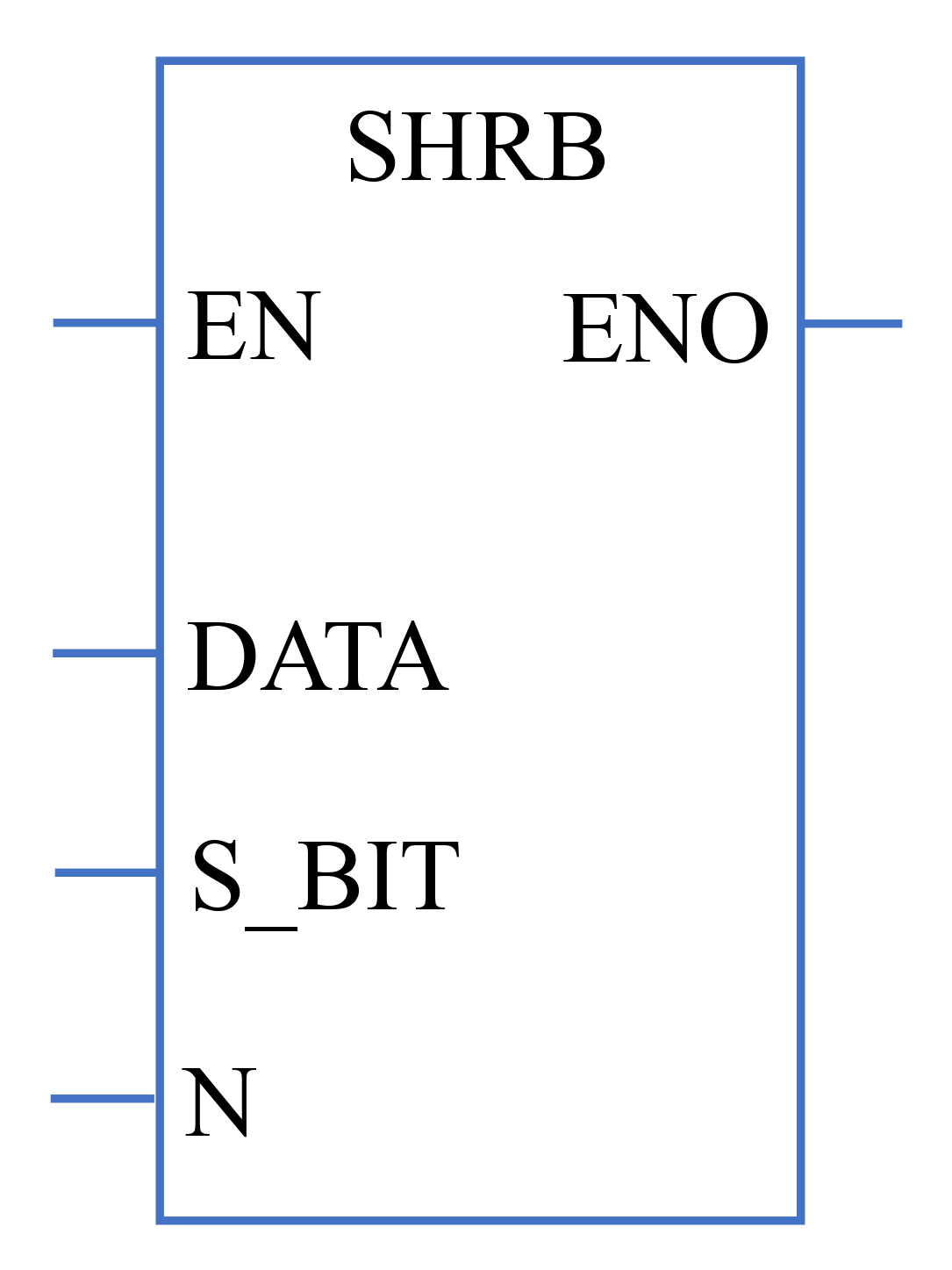

SHRB trong LAD

Lệnh xoay vòng thanh ghi theo kiểu BIT:

Khi đầu vào EN có một xung sẽ cho phép nhập dữ liệu từ đầu vào DATA vào thanh ghi dịch S_BIT

N số Bit trong thanh ghi dịch sẽ được nhập vào bit nhớ đặc biệt SM1.1

Các toán hạng:

- DATA, S_BIT: I, Q, M, SM, T, C, V, S, L

- N: VB, IB, QB, MB, SB, SMB, LB, AC, hằng số

Ngoài những biểu tượng (ký hiệu), cú pháp, câu lệnh cơ bản ở trên thì còn những câu lệnh khác, các bạn tự tìm hiểu tiếp ha.

Ví dụ chương trình LAD

Một số ví dụ về chương trình PLC được viết bằng ngôn ngữ lập trình Ladder:

- Hướng dẫn thiết kế giao diện Web Server cho PLC điều khiển & giám sát máy bơm công nghiệp

- Lập trình điều khiển & giám sát dây chuyền sản xuất thức ăn cho vật nuôi với PLC S7-1200 + WinCC + WebServer

- Lập trình điều khiển cánh tay robot bằng PLC S7-200 & Arduino

- Lập trình điều khiển & giám sát hệ thống phân loại sản phẩm theo chiều cao với S7-200, S7-300 & WinCC

Trên đây, MESIDAS đã chia sẻ cho các bạn những kiến thức cơ bản về ngôn ngữ lập trình LAD/LD (Ladder Logic/Ladder Diagram) cho PLC. Hy vọng rằng, với những thông tin ở phía trên sẽ giúp ích được cho các bạn trong quá trình nghiên cứu, tìm hiểu, học tập hay làm việc với ngôn ngữ lập trình LAD/LD (Ladder Logic / Ladder Diagram). Xin cảm ơn!